芯片分析问答25.6.26

- 2025-07-04 21:11:39

- 508

Q1

大家有遇到过MCU在运行中VDD键合丝熔断的情况吗?4根键合丝熔断3根,在ADC部分的GND通道上有热点。

A1

应该是内部短路后,引起的烧毁吧,剩下焊线是有焊点脱落开路吧,不然它怎么能不熔断,建议1.做一下浪涌,2.做全套的LU,芯片的其他管脚发生LU,也是表现在电源上大电流。

Q2

针对Shadow moire report实验,行业翘曲度标准大概是什么范围算合格?

A2

-/+80um,要看导入数据时框选位置,一般的84大概率是四角相对参考平面的值,要是角上放的是VSS或者Dummy,风险不高的,只看80是理论家的做法,款选位置对测量数据的影响较大,且框选是手动的,不能精确到具体的尺寸;Shadow moire 测量是热变形,温区曲线最好follow客户SMT曲线;84要具体看是高温区间,还是低温温区,高温区影响比低温区大一些。

Q3

一般产品都不做LTOL或者很少做,做HTOL比较多,那客户如果问起来为什么不做LTOL,可以怎么解释起来合理一些?另外根据HTOL的试验时间是不能等效到低温-40℃的寿命吧?低温有专门的寿命模型吗?

A3

LTOL主要失效模型是HCI,可以用Fab的HCI结果替代,HTOL和LTOL机理不同,不能等效,HTOL是多方面综合的,其中TDDB占多数。

Q4

帮忙推荐一下划片厂,要能经受客户验厂的那种,产品是硅片,MPW的,一片上有三种型号。

A4

可以找季丰,季丰可以做划片的。

Q5

一款芯片的抗ESD能力,有没有可能HBM很弱,但MM很强?

A5

有可能,我也见过,和设计的策略有关,主要是由于内部电路设计的差异、ESD保护策略的不同以及测试条件和标准的差异所导致的。

Q6

晶圆研磨供应商变更了,一般需要做什么验证?这个AEC-Q100里也没有对应的项目。

A6

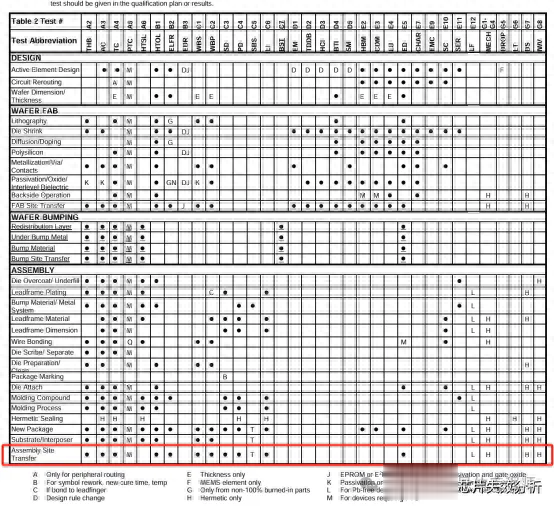

参考红框圈出的来做实验。

Q7

有没有人遇到过在不同机构测试ESD,Latch up结果不一样的?

A7

同一家机构,甚至同一台设备都碰到过结果不一样的,如果发现有这种现象,还是要多Debug,在一些对于某些参数敏感的时候,ESD测试起来还是有一些Options的。

Q8

TC用的两箱法,两个温区分别是-55,150℃,每个温区保存15min,机械传动材料的方式进行轮换,一个小时2个循环,这样是不是就做成热冲击了?正常那种带升温和降温的TC是怎么做的?

A8

高低温中间有个常温静置步骤。

Q9

对于wafer出货的IC,IC本身这边可靠性需要做些什么项目?客户那边拿我们的IC自己去进行合封。

A9

芯片本身肯定要先做开发板测ESD和HTOL那些可靠性,整wafer出货就主要靠CP良率来卡控了,另外就是靠WAT监控工艺波动,可靠性要求高的话,就得看做CP三温测试,另外要看有没有Flash,有Flash的话要做存储老化CP再出货。

Q10

有谁做过动态Latch up测试吗?哪里可以做?

A10

要罐pattern,这个需要机台的一个模块控制,目前几乎没有人做,所以市面上也几乎是没有去配这个模块,一般是单独定制测试板,给予一些外围电路,让IC工作再去做Latch up。

Q11

我用NaOH溶液去掉了铝线,那芯片上的黄色和灰色是什么材料?

A11

如果能提供更加清晰的照片会更加容易分辨,正常都是TIN,厚度不同在OM下的颜色深浅有差异。

Q12

下图这种白斑大家碰到过吗?是怎么造成的?

A12

是via位置的绿油分层起泡,找你们基板供应商。

Q13

在消费类产品做LU的过程中,什么情况下,需要在Tj=125度下进行测试,而不是常温下进行测试?

A13

一般是预留转车电的芯片会做一下。

Q14

如下为什么非要用陪片?

A14

验证环境是不是可靠。

Q15

对于车规TO MOS产品,N管和P管都要做AEC Q101认证吗?

A15

每个产品都要过认证,根据产品分类来看使用Q100,101,102,103,104。

Q16

长期存储的MSL1级产品需要考虑受潮问题吗?

A16

不用,MSL1的标准就是可以无限期放置的。

Q17

高温回流焊会导致功能失效,参数漂移吗?

A17

参数漂移会,功能失效不一定,当然会有功能失效风险,比如分层蹿锡短路,爆米花开路。

Q18

QNF封装BHAST做完2倍stress(192hrs)后出现分层的情况,有遇到过吗?按车规AEC-Q006的要求,这种算可接受吗?

A18

环境实验,是不卡分层的,只有MSL实验才卡分层,但是也要看具体分层情况,是否有非功能性失效,客户能否接受。

Q19

对于芯片的FIT值,是用来衡量芯片的哪个角度的指标呢?

A19

MTTF 和 λ,FIT越低越好,但是可以随着量产时间及样品数量的增加而降低的。

Q20

2.5D的封装成本比2D的封装成本增加几倍(在相同的5个die且基板差不多规格的情况下)?

A20

之前了解到Silicon interposer 2.5D价格应该是MCM的接近10X数量级了,具体价格case by case吧。

Q21

BGA产品锡球脱落(FT时发现),锡球脱落是有标准的吗,还是不允许锡球脱落?

A21

不允许锡球脱落的。

Q22

只有测芯片EMI的,那对于芯片的EMS有测试标准吗?

A22

本身芯片级的EMC就是个nice to have的测试,标准也没有规定go-no-go的曲线,都是让与终端客户协商来定,系统板子有很多手段治理EMI和EMS的问题,比如加屏蔽,加衰减泄放通路等,系统级必须要过强制的标准,有严格的标准曲线,但是也确实遇到过系统上很难解决的EMI问题,最后还是芯片改版解决的。

Q23

封装过程开帽发现丝状异物,大家有没有遇到过该异常?

A23

先做EDX看是什么东西,从分布来看,有点像劈刀磨损导致拉丝,如果是异物的话,很难有这种拐弯和这么好的韧性,导致molding注塑时都没有被冲开。

半导体工程师

半导体行业动态,半导体经验分享,半导体成果交流,半导体信息发布。半导体培训/会议/活动,半导体社群,半导体从业者职业规划,芯片工程师成长历程。

- 上一篇:游行抗议已扩散到美国多地

- 下一篇:中国网络文明大会来了